3. Simulation

시뮬레이션을 통해 해당 프로세서의 작동을 검증하고 확인한다.

3.1. Mips Top module simulation

설계한 Mips 5stage pipline processor가 제대로 작동되는지 확인하기 위한 명령어 예제로 1.2.3 Instruction Memory 에 적혀있는 예제 코드를 활용한다

사용한 테스트 벤치

| `timescale 1ns / 1ps module MIPS_tb(); reg clk, rst; wire [31:0] ProgramCounter_Output, t0, t1, t2, t3, t4, t5, t6, t7; wire [31:0] mem8, mem9, mem10, mem11, mem12, mem13, mem14, mem15; wire [1:0] forwardA, forwardB; wire hazard; MIPS uut ( .clk(clk), .rst(rst), .ProgramCounter_Output(ProgramCounter_Output), .Register_8(t0), .Register_9(t1), .Register_10(t2), .Register_11(t3), .Register_12(t4), .Register_13(t5), .Register_14(t6), .Register_15(t7), .memory_8(mem8), .memory_9(mem9), .memory_10(mem10), .memory_11(mem11), .memory_12(mem12), .memory_13(mem13), .memory_14(mem14), .memory_15(mem15), .forward_A(forwardA), .forward_B(forwardB), .hazard(hazard) ); initial begin clk = 0; rst = 1; #5 rst = 0; #200 $finish; end always #5 clk <= ~clk; endmodule |

첫 번째로, 초기값이 0으로 지정된 클락 신호 clk는 5 타임 유닛 간격으로 반전되어 클럭이 생성된다.

두 번째로, 초기값이 1로 설정된 리셋 신호 rst는 5 타임 유닛이 지난 후에 비활성화되어 리셋이 해제된다.

세 번째로, 5 타임 유닛 이후부터 200 타임 유닛까지 명령어가 MIPS 프로세서에 주입된다.

곧, 초기에는 클럭이 생성되고 리셋이 활성화된 상태에서 시작하여, 일정 시간 이후에 리셋이 해제되면서 명령어 주입이 시작된다.

1번 예제 소스 코드 실행 결과

첫번째 예제 코드는 beq instruction의 정상적 작동과 beq instruction 으로 발생한 Hazard 해결에 중점을 맞춘 코드이며, 정상적으로 작동함을 확인할 수 있다.

2번 예제 소스 코드 실행 결과

lw hazard가 발생하는 두 번째 예제도 정상적으로 작동하며, 이를 통해 해당 프로세서가 모든 Hazard를 적절히 해결하여 정상적으로 동작함을 확인할 수 있다.

3.2. UART 실행 결과

Case 1

(1) 실행 명령

| nop addi $8, $0, 8 addi $9, $0, 8 beq $8, $9, 100 add $11, $9, $8 add $11, $11, $9 add $10, $9, $8 addi $8, $8, 15 addi $9, $9, 5 slt $10, $9, $8 beq $8, $9, 10 sub $11, $8, $9 addi $8, $0, 15 addi $9, $0, 15 |

(2) 예상 출력 결과

| PC | Change |

| 000001a4 | $8 : 00000000 -> 00000008 |

| 000001a8 | $9 : 00000000 -> 00000008 |

| 000001ac | no change |

| 000001b0 | $10: 00000000 -> 00000010 |

| 000001b4 | $8 : 00000008 -> 00000017 |

| 000001b8 | $9 : 00000008 -> 0000000D |

| 000001bc | $10: 00000010 -> 00000001 |

| 000001c0 | no change |

| 000001c4 | $11: 00000000 -> 0000000A |

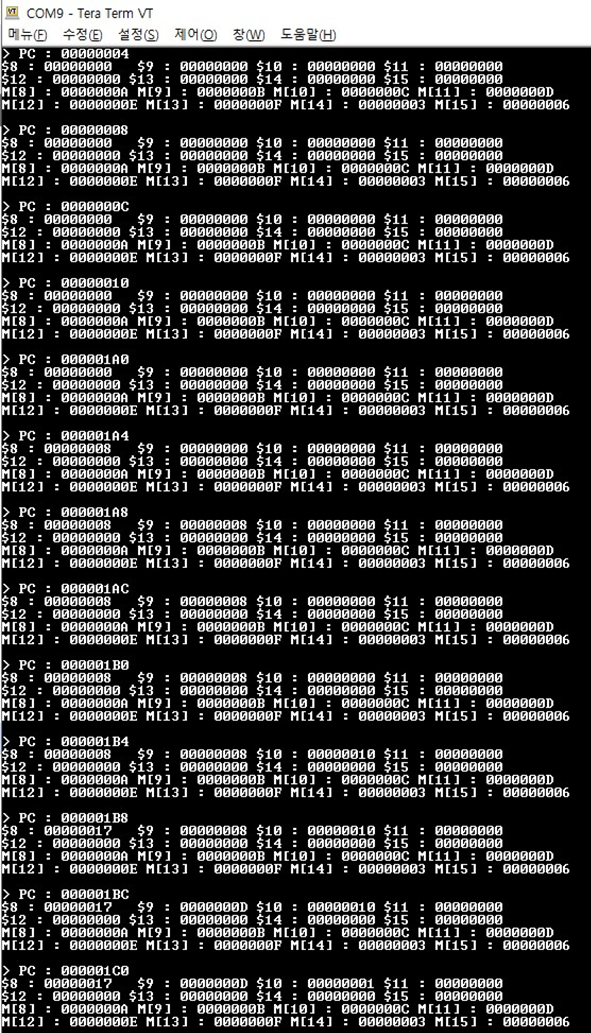

(3) TeraTerm 화면

Case 2

(1) 실행 명령

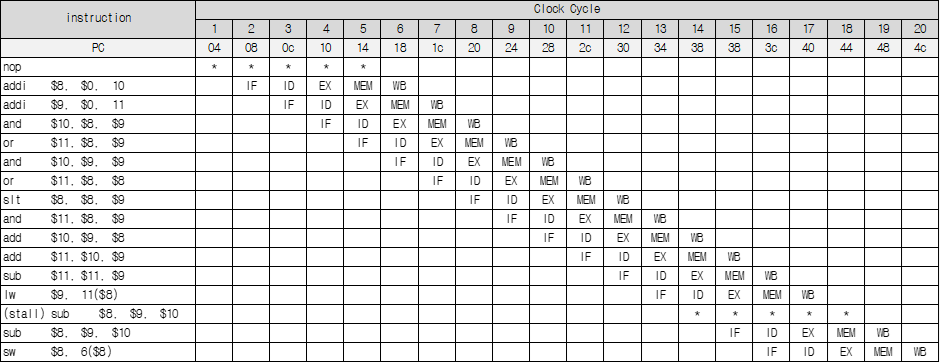

| nop addi $8, $0, 10 addi $9, $0, 11 and $10, $8, $9 or $11, $8, $9 and $10, $9, $9 or $11, $8, $8 slt $8, $8, $9 and $11, $8, $9 add $10, $9, $8 add $11, $10, $9 sub $11, $11, $9 lw $9, 11($8) sub $8, $9, $10 sw $8, 6($8) |

(2) 예상 출력 결과

| PC | Change |

| 00000018 | $8 : 00000000 -> 0000000A |

| 0000001c | $9 : 00000000 -> 0000000B |

| 00000020 | $10: 00000000 -> 0000000A |

| 00000024 | $11: 00000000 -> 0000000B |

| 00000028 | $10: 0000000A -> 0000000B |

| 0000002c | $11: 0000000B -> 0000000A |

| 00000030 | $8 : 0000000A -> 00000001 |

| 00000034 | $11: 0000000A -> 00000001 |

| 00000038 | $10: 0000000B -> 0000000C |

| 00000038 | $11: 00000001 -> 00000017 |

| 0000003c | $11: 00000017 -> 0000000C |

| 00000040 | $9 : 0000000B -> 0000000E |

| 00000044 | no change |

| 00000048 | $8 : 00000001 -> 00000002 |

| 0000004c | Mem[8] : 0000000A -> 00000002 |

(3) TeraTerm 화면

4. 결론

해당 프로젝트를 통하여 MIPS 5 stage Pipeline Processor을 Verilog로 성공적으로 설계하고 구현하였다. 목표는 효율적인 명령어 처리를 위한 파이프라인 아키텍처를 개발하는 것이었으며, 이를 달성하기 위해 여러 어려움을 극복했다

Utilization

Utilization report에 의하면 합성 결과 LUT는 전체 면적의 19.31%를 사용하고 있으며, Register의 경우 전체 면적의 27.24%를 사용하고 있는 것을 확인할 수 있다. Look-up table의 경우에는 string_gen 모듈에 의해 높은 사용량을 보이고 있다.

Timing

Timing Report에 의하면 WNS(Worst Negative Slack)이 2.893ns로 클럭으로 설정한 10 ns 안쪽으로 들어오는 것을 확인할 수 있다. 따라서 MIPS를 실행하면서 타이밍에 의한 문제는 없을 것으로 보인다.

설계 및 구현 개요

MIPS 5단계 파이프라인은 IF (Instruction Fetch), ID (Instruction Decode), EX (Execution), MEM (Memory Access), 그리고 WB (Write Back) 단계로 구성되어 효율적인 명령어 처리를 위한 아키텍처를 제공한다. 각각의 파이프라인 단계는 독립적으로 동작하며, Verilog를 사용하여 하드웨어 레벨에서 파이프라인을 구현하여 설계의 탄탄성과 성능을 확보하였다. 이러한 구현은 명령어 처리를 병렬로 수행하므로 전체적인 성능 향상을 도모하였다.

테스트와 검증

파이프라인의 각 단계에 대한 테스트 벤치마크를 도입하여 설계의 정확성을 검증했다. 다양한 MIPS 명령어를 사용하여 명령어 처리의 정확성과 성능을 테스트하였으며, 시뮬레이션 결과가 기대한 대로 나오는지 확인했다. 이 과정에서 얻은 피드백을 토대로 디자인을 수정하고 최적화하는 작업을 반복하여 안정성을 확보하였다.

성과 및 결과

구현된 MIPS 5 Stage Pipeline Processor는 기대한 대로 작동하며, 다양 Hazard를 해결하여 명령어 처리 속도와 효율성 면에서 향상된 결과를 얻었다. Forwarding과 같은 기술의 도입으로 인해 Data Hazard에 따른 지연 등이 최소화되어 전체 성능이 향상되었다.

향후 방향

향후 프로젝트 확장을 고려할 때, 현재의 프로세서를 더욱 강화하고 확장성을 높일 수 있는 다양한 측면이 있습니다. 첫째로, 더 복잡하고 다양한 명령어 세트를 지원하는 방향으로 나아갈 수 있다. Jal instruction, Bne instruction 등 많은 instruction을 추가하여 이를 통해 더 다양한 응용 분야에 대응할 수 있으며, 프로세서의 범용성을 향상시킬 수 있다.

두 번째로, 파이프라인 스테이지를 추가하여 명령어 처리의 병렬화를 더욱 깊게 할 수 있다. 새로운 스테이지를 도입함으로써 명령어 처리의 성능을 향상시킬 뿐만 아니라, IF_ID Register의 Stall을 최적화하여 추가 레지스터를 최소화하는 등의 작업을 통해 프로세서를 더욱 효율적으로 설계할 수 있다.

세 번째로, 외부에서 Memory를 직접 받아오는 방식을 도입하여 메모리 관리를 유연하게 구현할 수 있다. 이를 통해 메모리 크기의 확장이나 다양한 메모리 종류에 대한 대응이 가능해지며, 프로세서의 유연성이 증가할 것이다.

또한, 높은 동작 주파수에서도 효과적으로 동작할 수 있도록 하는 방법을 고려할 필요가 있다. 클럭 주기 최적화나 논리 구조의 개선을 통해 성능을 향상시키면서도 안정성을 유지하는 방향으로 연구를 진행할 수 있다. 높은 동작 주파수에서의 안정성은 프로세서의 성능을 한 단계 더 끌어올릴 수 있는 핵심적인 요소이다.

이러한 방향성들을 통해 미래의 프로젝트에서는 보다 강력하고 효율적인 하드웨어 아키텍처를 개발할 수 있을 것으로 기대된다. 이는 기존 프로젝트의 성공을 바탕으로 한 발전된 버전을 만들어 나가는 과정이 될 것이다.

마무리

이 프로젝트를 통해 MIPS 5단계 파이프라인의 설계 및 구현 과정에 대한 풍부한 경험을 쌓을 수 있었다. 결과적으로, 효율적이고 확장 가능한 하드웨어 아키텍처를 구축하는 데 성공했으며, 이는 미래의 프로젝트에 대한 강력한 기초를 제공한다. 이 경험을 통해 하드웨어 디자인 및 최적화에 대한 통찰력을 키우고, 더 높은 수준의 프로젝트에 도전해 나갈 수 있을 것이다.

참고 문헌

David Patterson, John Hennessy, 『Computer Organization and Design, 5/E The Hardware/Software Interface』, Morgan Kaufmann, 2013

개인 소감

프로젝트 시작 단계에서는 막막하고 불확실한 부분이 많았습니다. 설계를 진행하면서 프로젝트를 어떻게 완성할지에 대한 부담감도 컸습니다. 특히 Datapath를 그리고 각 모듈을 하나씩 만들어 가는 과정에서 해당 기능이 제대로 작동할지에 대한 불안감이 있었습니다. Program Counter, Instruction Memory 등의 모듈을 만들면서 하나의 파이프라인 스테이지를 완성하고, 이 단계가 정상적으로 동작하며 파이프라인을 통해 연결되는 과정을 보면서 설계에 대한 자신감을 키울 수 있었습니다.

설계 도중에는 어려운 부분들이 있었습니다. 첫 번째로는 Mips Top 모듈의 Port를 연결하는 과정에서 400줄이 넘는 코드로 인해 많은 어려움을 겪었습니다. Port와 wire의 이름이 유사해서 올바르게 연결되었는지 확인하기 어려웠고, 잘못 연결하여 테스트벤치에서 오류가 발생하기도 했습니다. 하지만 PPT를 활용하여 Datapath에 직접 입출력 Port와 wire 변수 명을 체계적으로 기록하고 확인하면서 하나씩 연결해 나가니 복잡한 작업도 차근차근 해결할 수 있었습니다.

두 번째 어려운 부분은 디버깅 과정이었습니다. Datapath는 완성되었지만 프로세서가 올바르게 작동하지 않아 디버깅에 많은 시간이 소요되었습니다. Data Hazard가 제대로 작동되지 않아 Forwarding이 이루어지지 않아서, 초기에는 Hazard가 발생할 경우 Program Counter의 값이 16씩 증가해야만 프로세서가 제대로 동작했습니다. Beq instruction에서도 데이터 위험이 발생할 경우 제대로 작동하지 않았고, 이에 대응하기 위해 Branch Forwarding Unit을 추가하고 ID_Stage에 Branch Equal을 포함시키는 등의 수정이 이루어졌습니다. 이러한 수정 작업으로 인해 프로세서의 최종 모습이 완성되기까지 다양한 변화가 있었습니다.

세 번째로 어려웠던 부분은 관련 자료가 부족하여 스스로 만들어가야 했다는 점이었습니다. 특히 오디오 인터페이스를 제작할 때 소리를 어떻게 생성해야 할지에 대한 정보가 전혀 없었고, 해당 알고리즘을 찾아내고 구현하는 데에 어려움을 겪었습니다.

추가 어려웠던 점으로 처음에 ID Stage를 만드는데 그냥 모듈을 하나씩 하나씩 만들고 붙인게 전부인 것 같은데 이것이 제대로 작동될지에 대한 불안감이였습니다. 전부 만들기 전까지는 확실한 검증도 불가능하였기에 기도하면서 제발 되길 빌면서 만들었던 것 같습니다. 기말고사 기간과 겹쳐서 어느정도 기말고사 공부를 포기하면서 만들었고 종강하고 1주일동안 학교에서 잘 곳도 없이 도서관에서 자거나 자는 시간 줄여가면서 학교에서 만들고 있었던 것도 어려웠던 점 중 하나입니다.

이러한 어려움들을 극복하면서 해당 문제들을 해결하는 과정에서 쌓은 지식들이 더욱 자신의 것으로 만들어졌습니다. 특히 MIPS 5 Stage Pipeline을 완성하고 나니 이제야 제대로 구동되고 설계되어야 하는 방법에 대한 이해가 더욱 명확해진 것 같습니다. 이러한 경험을 토대로 더욱 심화된 내용을 공부하고 탐구하며 성장해 나가고 싶습니다.

이번 프로젝트를 성공적으로 완료할 수 있었던 것은 팀원의 도움이 컸습니다. 그 덕분에 프로젝트를 잘 마무리할 수 있었고, 그 도움에 감사하게 생각하고 있습니다. 또한 이런 소중한 경험을 할 수 있게 해주신 교수님께도 감사의 말씀을 전합니다.

'전공 이야기 > Digital System Design' 카테고리의 다른 글

| #7 MIPS Pipeline Processor Design (5) - I/O, Constraints (1) | 2023.12.26 |

|---|---|

| #6 MIPS Pipeline Processor Design (4) - Hazard, Top module (0) | 2023.12.26 |

| #5 MIPS Pipeline Processor Design (3) - Pipes, Control (0) | 2023.12.26 |

| #4 MIPS Pipeline Processor Design (2) - ID, EX, MEM, WB (1) | 2023.12.26 |

| #3 MIPS Pipeline Processor Design (1) - IF Stage, Sub Unit (0) | 2023.12.26 |